Make this article seo compatible,Let there be subheadings for the article, be in french, create at least 700 words

Les nœuds de processus d’Intel passeront de 20A cette année à 14A d’ici 2027

Intel lancera son nœud de processus 18A l’année prochaine

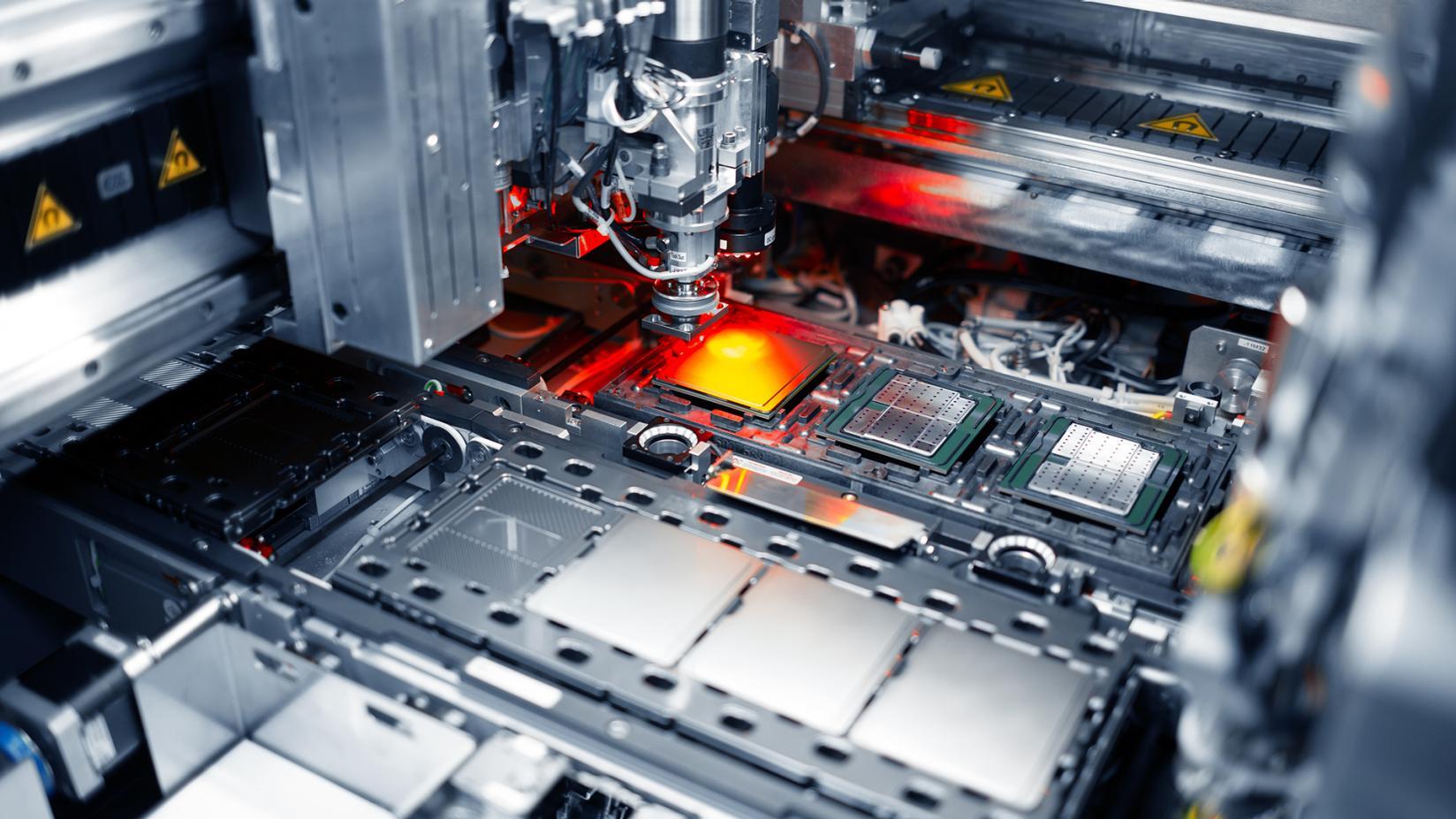

Mais à partir de sa production de 20A plus tard cette année, Intel aura un peu d’avance sur TSMC et Samsung Foundry avec une fonctionnalité clé que le fabricant de puces américain appelle PowerVia (également connue sous le nom de backside power delivery). TSMC devrait utiliser cette technologie avec son nœud N2P qu’il utilisera à partir de 2026. Samsung Foundry est censé utiliser l’alimentation électrique arrière sur un nœud particulier lancé l’année prochaine, bien que Samsung Foundry ne l’ait pas confirmé.

Alors, qu’est-ce que PowerVia ? La plupart des petits fils qui alimentent une puce se trouvent au-dessus de toutes les couches qui composent un composant en silicium. À mesure que ces puces deviennent plus puissantes et plus complexes, les fils supérieurs qui se connectent aux sources d’alimentation entrent en concurrence avec les fils qui connectent les composants. Cela entraîne un gaspillage d’énergie et un faible rendement.

PowerVia déplace les fils alimentant les puces vers l’arrière de la puce. En conséquence, les vitesses d’horloge peuvent augmenter de 6 %, ce qui entraîne de meilleures performances. Ajoutez à cela l’augmentation des performances obtenue grâce à l’utilisation d’un nœud de processus plus avancé, et le résultat est une puce plus puissante utilisée pour exécuter un appareil plus puissant.

Intel est le premier à prendre livraison de sa machine de lithographie ultraviolette extrême High-NA

Le PDG d’Intel, Gelsinger, a déclaré : « J’ai parié toute l’entreprise sur le 18A. » Intel s’attend à ce que les performances et l’efficacité de son nœud 18A soient supérieures à celles de TSMC. Intel a également signé un accord avec Arm permettant aux clients concepteurs de puces d’Arm de construire des SoC basse consommation à l’aide du nœud de processus 18A d’Intel. Le mois dernier, Intel a accepté de construire une puce personnalisée pour Microsoft en utilisant son procédé 18A. Quatre grandes entreprises anonymes (il n’est pas clair si Microsoft est l’une des quatre) ont signé pour qu’Intel produise leurs puces en utilisant le procédé 18A.

Les anciennes machines EUV ont une ouverture de 0,33 (équivalent à une résolution de 13 nm) et les machines High-NA ont une ouverture de 0,55 (équivalent à une résolution de 8 nm). Avec un motif de résolution plus élevée transféré sur une tranche, la fonderie pourrait éviter d’avoir à faire passer une tranche deux fois dans la machine EUV pour ajouter des fonctionnalités supplémentaires, économisant à la fois du temps et de l’argent. Alors que TSMC et Samsung Foundry ont tous deux commandé l’une des machines High-NA à ASML, Intel pourra probablement utiliser en premier la machine de lithographie qui permet de gagner du temps.